Chapter 3 Page tables

页表让每个进程都拥有自己独立的虚拟内存地址,并决定每个进程可以访问物理内存的哪些部分。

页表隔离了不同进程的地址空间,实现了内存隔离,并将它们映射到同一个物理内存

xv6通过页表实现了一些有趣的功能:在多个地址空间中映射相同的内存(a trampoline page 蹦床页面),并使用未映射的页面保护内核和用户堆栈。

3.1 Paging hardware

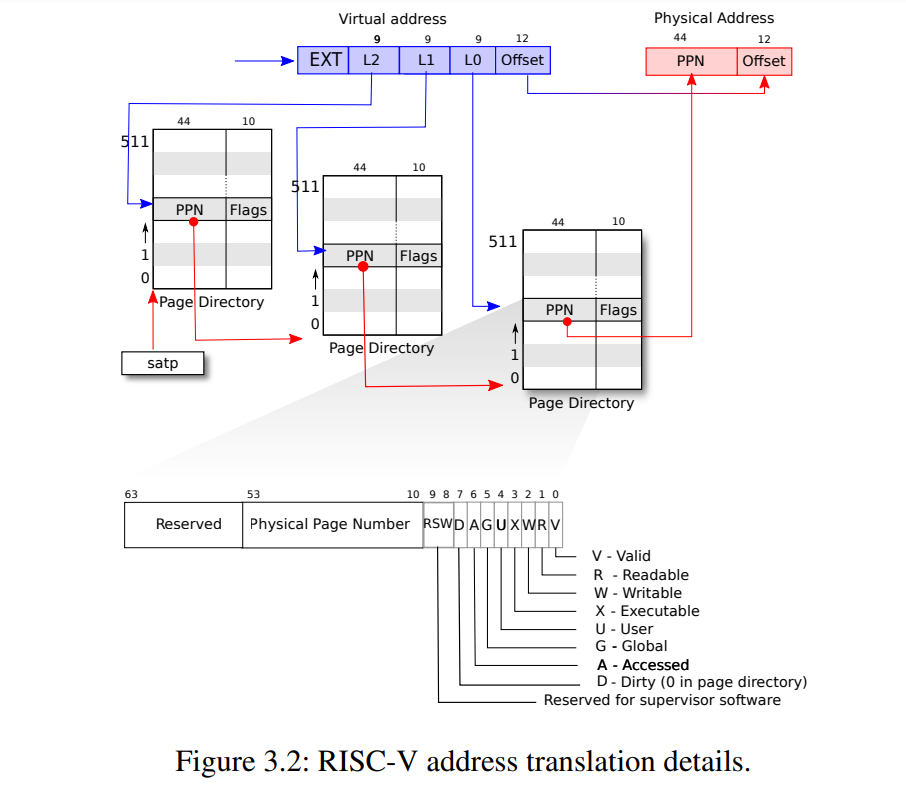

RISC-V指令操纵虚拟地址,而机器RAM或物理内存使用物理地址,RISC-V页表硬件通过将每个虚拟地址映射到物理地址来连接这两种地址

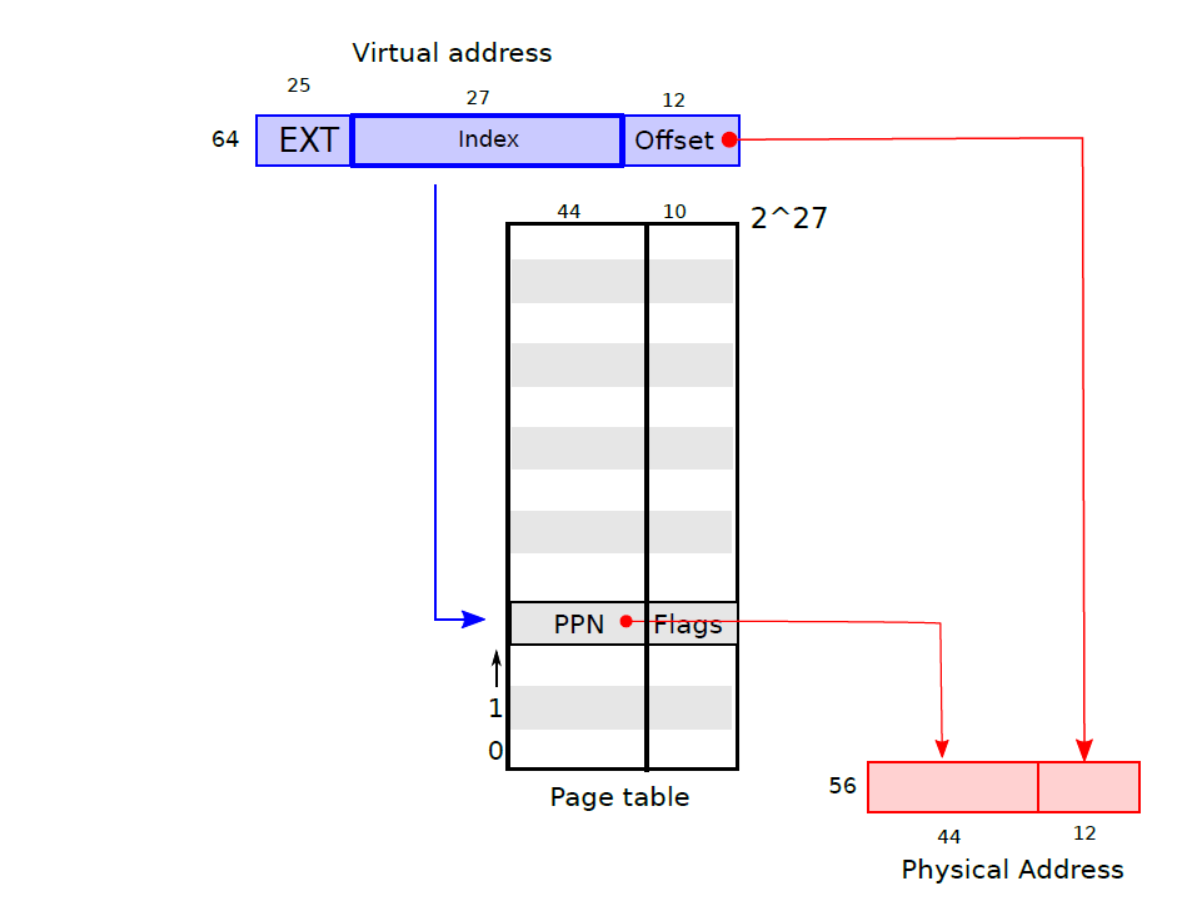

xv6运行于Sv39 RISC-V,即在 64 位地址中只有最下面的 39 位被使用作为虚拟地址,其中底 12 位是页内偏移,高 27 位是页表索引,即 4096 字节( $2^{12}$ )作为一个page,一个进程的虚拟内存可以有 $2^{27}$ 个page,对应到页表中就是 $2^{27}$ 个page table entry(PTE)。

每个PTE有一个 44 位的physical page number (PPN) 用来映射到物理地址上和 10 位flag,总共需要 54 位,用 8 个字节存储(下面解释)。每个物理地址的高 44 位是页表中存储的PPN,低 12 位是页内偏移,一个物理地址总共由 56 位构成。

在Sv39 RISC-V,PTE格式中存在着可以使物理地址再增加 10 位的空间。

在实际中,页表并不是作为一个包含了 $2^{27}$ 个PTE的大列表存储在物理内存中的,而是采用了三级树状的形式进行存储,这样可以让页表分散存储。每个页表就是一页。第一级页表是一个 4096 字节的页,包含了 512 个PTE(因为每个PTE需要 8 字节),每个PTE存储了下级页表的页物理地址。第二级列表由512个页构成,第三级列表由512*512个页构成。

与单层设计相比,三层结构可以以一种内存高效的方式记录PTE

通常情况下执行一个进程,大部分的虚拟地址是不会被映射的,三层结构可以省略整个页面目录

例如,如果一个应用程序只使用从地址 0 开始的几个页面,那么一级页面目录的条目 1 到 511 是无效的,因此内核不必为 1-511 的二级页面目录分配页面。此外,内核还不必为这些二级页面目录对应的的三层页面目录分配页面。因此,在本例中,三层结构为二级页面目录节省了511页,为底层页面目录节省511×512页。

因为每个进程虚拟地址的高 27 位用来确定PTE,对应到3级页表就是最高的 9 位确定一级页表PTE的位置,中间 9 位确定二级页表PTE的位置,最低 9 位确定三级页表PTE的位置。如下图所示。第一级根页表的物理页地址存储在satp寄存器中,每个CPU拥有自己独立的satp